Optimal Digital Implementation of Fractional-Order Models in a Microcontroller

Abstract

:1. Introduction

2. Plant Models

- First-order plus dead time (FOPDT)where denotes the gain of the model, is a time constant and is the delay of the plant.

- Second-order plus dead time (SOPDT)

- Non-integer-order plus dead time (NIOPDT)where denote constants and values of fractional orders.

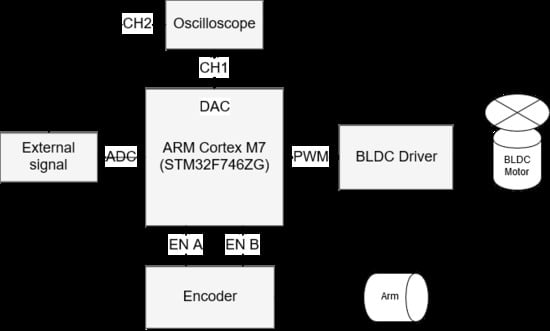

- maximum value of the main clock frequency MHz,

- analog-to-digital converter (ADC) synchronized with the internal timer interrupt routine (ISR) to sample the input signal on an ADC pin at kHz,

- number of ADC domain clock cycles required for a single ADC conversion providing the best possible accuracy of 12-bit resolution. Time of conversion ,

- single-precision hardware floating-point unit (FPU) and compiler warnings on automatic double-precision promotion enabled (software-simulated support for double-precision arithmetic),

- 60 Hz PWM output signal with adjustable duty cycle for driving the 11VDC-supplied micro-BLDC driver.

3. Discretization

- Discrete first-order plus dead time (DFOPDT)where and are numerator and denominator coefficients, respectively, and is the number of delay input samples at a given sample rate . The exact values of the coefficients are presented in Table 1.

- Discrete second-order plus dead time (DSOPDT)

- Discrete non-integer-order plus dead time (DNIOPDT)Discretization of the non integer-order transfer function (3) was performed in three consecutive steps. First, approximation of the transfer function in the frequency domain was obtained by applying Oustaloup’s Recursive filter algorithm (ORA) [10,18], approximating the complex variable s of the fractional order 0 < < 1, using the following formula:where denotes the frequency range of the approximation, N is the order and . As a result, function (6) generates poles and zeros in total. If then is first replaced with , where n is an integer number and u is a fractional part, approximated by the algorithm. Different values for the approximation order N were tested over the selected frequency range Step response and Bode characteristics for are presented in Figure 3 and Figure 4. It is noticeable that all values of the order N provide satisfactory approximations of the initial fractional order transfer function. Nevertheless, we proceeded with approximation orders . Since the approximation polynomials had over 14 zeros and poles, in the second step, a reduction was performed using the balancing reduction technique [19], available in MATLAB as balred method. Minimization of the cost functions for a new reduced-order plant model of a fixed balred order revealed that of several ORA filters, approximation of the order ensured the best match between both characteristics.

4. Implementation Difficulties

5. Time-Domain Approach Using the Grünwald–Letnikov Differintegral Operator and SMP

5.1. Initial Implementation- Look-up Tables, Shifted Input/Output Samples

5.2. Replacing Arrays with Ring Buffers

5.3. Enabling Optimization Flags

5.4. Enabling Hardware FPU Unit, Using CMSIS DSP Library

5.5. Other Approaches

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

Abbreviations

| ADC | analog-to-digital converter |

| BLDC | brushless direct-current motor |

| CYCCNT | Data Watchpoint and Trace Cycle Count Register |

| (D)FOPDT | (discrete) first-order plus dead time |

| (D)NIOPDT | (discrete) non-integer-order plus dead time |

| (D)SOPDT | (discrete) second-order plus dead time |

| FIR | finite impulse response |

| FO | fractional-order |

| FOC | fractional-order calculus |

| FOTF | fractional-order transfer function |

| FPU | floating-point unit |

| GL | Grünwald-Letnikov |

| IAE | integral absolute error |

| IIR | infinite impulse response |

| IO | integer-order |

| ISE | integral square error |

| ISR | interrupt service routine |

| MaxAPE | maximum absolute percentage error |

| MCU | microcontroller unit |

| ORA | Oustaloup Recursive Approximation |

| SIMD | Single Instruction Multiple Data |

| SMP | Short Memory Principle |

| UAV | unmanned aerial vehicle |

| (V)FOPID | (variable) fractional-order proportional-integral-derivative controller |

References

- Kilbas, A.A.; Srivastava, H.; Trujillo, J.J. Theory and Applications of Fractional Differential Equations; Elsevier Science Inc.: New York, NY, USA, 2006; Volume 204. [Google Scholar] [CrossRef]

- Miller, K.S.; Ross, B. An Introduction to the Fractional Calculus and Fractional Differential Equations; John Wiley & Sons: New York, NY, USA, 1993. [Google Scholar]

- Podlubny, I. Fractional Differential Equations. An Introduction to Fractional Derivatives, Fractional Differential Equations, to Methods of their Solution and some of their Applications; Academic Press: San Diego, CA, USA, 1999. [Google Scholar]

- Merrikh-Bayat, F.; Mirebrahimi, N.; Khalili, M.R. Discrete-time fractional-order PID controller: Definition, tuning, digital realization and some applications. Int. J. Control Autom. Syst. 2015, 13, 81–90. [Google Scholar] [CrossRef]

- Petráš, I.; Vinagre, B.M. Practical application of digital fractional-order controller to temperature control. Proc. Acta Montan. Slovaca 2002, 7, 131–137. [Google Scholar]

- Tepljakov, A.; Petlenkov, E.; Belikov, J. Embedded system implementation of digital fractional filter approximations for control applications. In Proceedings of the 21st International Conference on Mixed Design of Integrated Circuits and Systems (MIXDES 2014), Lublin, Poland, 19–21 June 2014. [Google Scholar] [CrossRef]

- Tepljakov, A.; Petlenkov, E.; Belikov, J.; Finajev, J. Fractional-order controller design and digital implementation using FOMCON toolbox for MATLAB. In Proceedings of the IEEE International Symposium on Computer-Aided Control System Design, Hyderabad, India, 28–30 August 2013. [Google Scholar] [CrossRef]

- Dziwiński, T.; Pia̧tek, P.; Baranowski, J.; Bauer, W.; Zagórowska, M. On the practical implementation of non-integer order filters. In Proceedings of the 2015 20th International Conference on Methods and Models in Automation and Robotics (MMAR), Miedzyzdroje, Poland, 24–27 August 2015; pp. 921–924. [Google Scholar] [CrossRef]

- MacDonald, C.L.; Bhattacharya, N.; Sprouse, B.P.; Silva, G.A. Efficient computation of the Grünwald–Letnikov fractional diffusion derivative using adaptive time step memory. J. Comput. Phys. 2015, 297, 221–236. [Google Scholar] [CrossRef] [Green Version]

- Oustaloup, A. La commande CRONE: Commande Robuste D’ordre non Entier; Hermes: Paris, France, 1991. [Google Scholar]

- Vinagre, B.M.; Podlubny, I.; Hernandez, A.; Feliu, V. Some approximations of fractional order operators used in control theory and applications. Fract. Calc. Appl. Anal. 2000, 3, 231–248. [Google Scholar] [CrossRef] [Green Version]

- Garrappa, R. Numerical Solution of Fractional Differential Equations: A Survey and a Software Tutorial. Mathematics 2018, 6, 16. [Google Scholar] [CrossRef] [Green Version]

- Tepljakov, A.; Petlenkov, E.; Belikov, J. FOMCON: Fractional-Order Modeling and Control Toolbox for MATLAB. In Proceedings of the 18th International Conference “Mixed Design of Integrated Circuits and Systems” (MIXDES 2011), Gliwice, Poland, 16–18 June 2011; pp. 684–689. [Google Scholar] [CrossRef]

- Alagoz, B.B.; Tepljakov, A.; Ates, A.; Petlenkov, E.; Yeroglu, C. Time-domain identification of One Noninteger Order Plus Time Delay models from step response measurements. Int. J. Model. Simul. Sci. Comput. 2019, 10. [Google Scholar] [CrossRef]

- STMicroelectronics. STM32F745xx STM32F746xx ARM-based Cortex-M7 32b MCU+FPU, 62DMIPS up to 1MB Flash/320+16+4KB RAM, USB OTG HS/FS, ethernet, 18TIMs, 3ADCs, 25 com itf, cam & LCD Datasheet. 2016. Available online: https://www.st.com/resource/en/datasheet/stm32f746zg.pdf (accessed on 9 March 2020).

- Monje, C.A.; Chen, Y.; Vinagre, B.M.; Xue, D.; Feliu, V. Fractional-order Systems and Controls Fundamendals and Applications. In Advances in Industrial Control; Springer: London, UK, 2010. [Google Scholar] [CrossRef]

- Lyons, R.G. Understanding Digital Signal Processing; Prentice Hall PIR: Upper Saddle River, NJ, USA, 2004. [Google Scholar]

- Oustaloup, A. La dérivation non entière: Théorie, Synthèse et Applications; Hermes: Paris, France, 1995. [Google Scholar]

- Caponetto, R.; Machado, J.T.; Murgano, E.; Xibilia, M.G. Model Order Reduction: A Comparison between Integer and Non-Integer Order Systems Approaches. Entropy 2019, 21, 876. [Google Scholar] [CrossRef] [Green Version]

- Garrappa, R.; Kaslik, E.; Popolizio, M. Evaluation of Fractional Integrals and Derivatives of Elementary Functions: Overview and Tutorial. Mathematics 2019, 2, 407. [Google Scholar] [CrossRef] [Green Version]

- Wei, Y.; Chen, Y.; Cheng, S.; Wang, Y. A note on short memory principle of fractional calculus. Fract. Calc. Appl. Anal. 2017, 20. [Google Scholar] [CrossRef]

- Chen, Y.; Petráš, I.; Xue, D. Fractional order control—A tutorial. In Proceedings of the American Control Conference, St. Louis, MO, USA, 10–12 June 2009. [Google Scholar] [CrossRef]

- ARM Ltd. ARM Cortex-M7 Processor, r0p2 ed.; ARM Ltd.: Cambridge, UK, 2014; Available online: http://infocenter.arm.com/help/topic/com.arm.doc.ddi0489b/DDI0489B_cortex_m7_trm.pdf (accessed on 9 March 2020).

- ARM Ltd. Arm® Compiler Version 6.12 User Guide; ARM Ltd.: Cambridge, UK, 2019. [Google Scholar]

- STMicroelectronics. AN4044 Application Note. Floating Point Unit Demonstration on STM32 Microcontrollers. 2016. Available online: https://www.st.com/content/ccc/resource/technical/document/application_note/10/6b/dc/ea/5b/6e/47/46/DM00047230.pdf/files/DM00047230.pdf/jcr:content/translations/en.DM00047230.pdf (accessed on 9 March 2020).

| Coeff | |||

|---|---|---|---|

| 1.123629474892 × 10−4 | 2.90801788577010 × 10−6 | 0.00141997809862250 | |

| 1.901155870198 × 10−3 | 6.60568256821855 × 10−6 | ||

| 9.979752146549 × 10−1 | 1.993748864318110 | 2.99589971448314 | |

| - | 0.25547387436067 × 10−6 | 0.00428081749129811 | |

| - | |||

| - | - | ||

| - | - | 0.995906835027740 | |

| 1228 | 1065 | 1000 |

| ISE | IAE | ITSE | ITAE | NRMSE | MaxAPE | |

|---|---|---|---|---|---|---|

| - | - | - | - | - | - | |

| 99.91% | 0.12% | |||||

| 99.24% | 0.65% | |||||

| 98.31% | 1.25% | |||||

| 98.01% | 1.43% | |||||

| 87.53% | 6.60% | |||||

| 0.00% | 46.57% | |||||

| 99.83% | 12.22% | |||||

| 99.82% | 12.20% | |||||

| 99.82% | 12.66% |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Matusiak, M.; Bąkała, M.; Wojciechowski, R. Optimal Digital Implementation of Fractional-Order Models in a Microcontroller. Entropy 2020, 22, 366. https://0-doi-org.brum.beds.ac.uk/10.3390/e22030366

Matusiak M, Bąkała M, Wojciechowski R. Optimal Digital Implementation of Fractional-Order Models in a Microcontroller. Entropy. 2020; 22(3):366. https://0-doi-org.brum.beds.ac.uk/10.3390/e22030366

Chicago/Turabian StyleMatusiak, Mariusz, Marcin Bąkała, and Rafał Wojciechowski. 2020. "Optimal Digital Implementation of Fractional-Order Models in a Microcontroller" Entropy 22, no. 3: 366. https://0-doi-org.brum.beds.ac.uk/10.3390/e22030366