Parasitic Capacitance Effects on Active Clamp Flyback Output Characteristics: Application to IPOP Connection

Abstract

:1. Introduction

- Obtaining an analytical expression that relates the output voltage to the output current when there are no parasitic elements, i.e., the converter output characteristics, which show how modules can share the current and the effects of the tolerances;

- Obtaining the output characteristics, including the parasitic terms, and comparing them to data that were obtained using simulations (since they are based on parameters that are difficult to measure in practice);

- An in-depth analysis of the new topology using the clamp that was proposed in [24], which describes and studies the stages within a cycle;

- Obtaining an analytical expression of the output characteristics when the clamp diode is incorporated, including the parasitic elements, and its validation using simulations;

- Comparing the output characteristics when the clamp diode and parasitic elements are included to find the ideal configuration. Using this, it can be checked that they are quite close, even for large variations in the parasitic capacities.

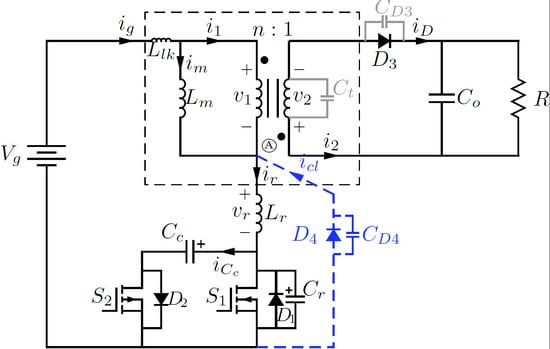

2. Analysis of Active Clamp Flyback Converter

2.1. Load Sharing under Ideal Behavior

- Time interval : Prior to , was on and the same constant current was passing through and and . When the main switch was turned off at , the resonant current charged very quickly. After that, the current was directed to the clamp capacitor through the auxiliary diode and the auxiliary switch could be switched on at zero voltage. The output diode was forward-biased at this point and energy could be transferred to the output through the coupled inductors. The current was identified as the reversed secondary side current and was related to the primary current by a factor of n. On the other side, and exchanged energy in a resonant way. The resonant current became reversed and had a negative value at the end of this interval.

- Time interval : At , was switched off and the resonant current evolved from , a negative value, into a positive value under constant voltage for the majority of the time. Firstly, the resonant current helped to discharge very quickly. Secondly, the resonant current flowed across , thereby allowing a zero voltage switching of the main switch before became a zero value. Finally, when obtained a positive value, it flowed through until it matched to magnetizing current at . The output diode was reverse-biased at this moment.

- Time interval : From to the end of the switching period at , the same current was passing through and , which increased their stored energy.

2.2. Introducing the Effects of Parasitics

2.3. Output Characteristic Curves

3. Enhanced ACF Topology

3.1. Operating Principles

- Time interval 1 ( Figure 6a): Prior to , the same current flowed through and . It comprised the magnetizing current I and the current from the diode branch . The main switch was turned off at and the resonant current rapidly charged until its voltage reached .

- Time interval 2 ( Figure 6b): After charging , the resonant current was redirected to through the auxiliary diode . exchanged energy with the clamp capacitor while the current decreased linearly to arrive at the value of I at . At this point, the current through became zero and was off.

- Time interval 3 ( Figure 6c): The resonant current decreased through capacitors and until the voltage in reached at . At this moment, was forward biased.

- Time interval 4 ( Figure 6d): Once started to conduct, energy was transferred to the output and the voltage that was applied to the resonant inductor became a negative value . Then, the resonant current was flowing through and decreased linearly until it reached zero value. To achieve the zero voltage switching of the auxiliary switch , it was necessary to turn on the transistor before the end of this interval, i.e., while its body diode was conducting.

- Time interval 5 ( Figure 6e): During this interval, circulated through the main body of until was switched off at . The resonant current decreased from zero to a negative value of .

- Time interval 6 ( Figure 6f): During this short time interval, the resonant current helped to discharge very quickly to zero voltage and barely changed its value.

- Time interval 7 ( Figure 6g): During this interval, the resonant current initially flowed across . It evolved from a negative value into a zero value under the constant voltage . To achieve the zero voltage switching of , it was required to turn on the transistor before the end of this interval.

- Time interval 8 ( Figure 6h): The resonant current evolved from a zero value into a positive value under the constant voltage and it circulated through the main body of until , at which point the resonant and magnetizing current equaled I. The output diode was reverse-biased.

- Time interval 9 ( Figure 6i): The energy that was stored in during interval 3 was returned to in a resonant form, which led to a current increment that was equal to at the final instant .

- Time interval 10 ( Figure 6j): From to the end of the switching period at , the same current was passing through and . The energy that was stored in and increased at the same time.

3.2. Steady-State Analysis

3.3. Output Characteristic Curves

- Regarding the real ACF curves, there was an important difference when the clamp diode was employed. Horizontal zones did not appear for the EAC when the parasitics were considered, which was an advantage when equal load sharing was required;

- The EACF curves were slightly affected by substantial changes in the parasitic capacitances. Then, load sharing was feasible independently of the parasitics because of its minor influence;

- The EACF curves had similar trends to those of the ideal ACF. Nevertheless, the duty cycle was different, although the operation parameters were identical. Moreover, for the enhanced topology, a smaller duty cycle was required to reach the same output voltage and current.

4. Experimental Results

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Knabben, G.C.; Zulauf, G.; Schäfer, J.; Kolar, J.W.; Kasper, M.J.; Azurza Anderson, J.; Deboy, G. Conceptualization and Analysis of a Next-Generation Ultra-Compact 1.5-kW PCB-IntegratedWide-Input-Voltage-Range 12V-Output Industrial DC/DC Converter Module. Electronics 2021, 10, 2158. [Google Scholar] [CrossRef]

- Kasper, M.; Bortis, D.; Kolar, J.W. Scaling and balancing of multi-cell converters. In Proceedings of the IEEE International Power Electronics Conference (IPEC-Hiroshima 2014—ECCE ASIA), Hiroshima, Japan, 18–21 May 2014; pp. 2079–2086. [Google Scholar] [CrossRef]

- Luo, S. A review of distributed power systems part I: DC distributed power system. IEEE Aerosp. Electron. Syst. Mag. 2005, 20, 5–16. [Google Scholar] [CrossRef]

- Roy, S.; Joisher, M.; Hanson, A.J. A Decentralized Nonlinear Control Scheme for Modular Power Sharing in DC-DC Converters. In Proceedings of the 2021 IEEE Energy Conversion Congress and Exposition (ECCE), Vancouver, BC, Canada, 10–14 October 2021; pp. 2798–2805. [Google Scholar] [CrossRef]

- Chen, W.; Ruan, X.; Yan, H.; Tse, C.K. DC/DC Conversion Systems Consisting of Multiple Converter Modules: Stability, Control, and Experimental Verifications. IEEE Trans. Power Electron. 2009, 24, 1463–1474. [Google Scholar] [CrossRef]

- Cheng, J.; Shi, J.; He, X. A novel input-parallel output-parallel connected DC-DC converter modules with automatic sharing of currents. In Proceedings of the 7th International Power Electronics and Motion Control Conference, Harbin, China, 2–5 June 2012; Volume 3, pp. 1871–1876. [Google Scholar] [CrossRef]

- Shi, J.; Zhou, L.; He, X. Common-Duty-Ratio Control of Input-Parallel Output-Parallel (IPOP) Connected DC-DC Converter ModulesWith Automatic Sharing of Currents. IEEE Trans. Power Electron. 2012, 27, 3277–3291. [Google Scholar] [CrossRef]

- Luo, S.; Ye, Z.; Lin, R.L.; Lee, F. A classification and evaluation of paralleling methods for power supply modules. In Proceedings of the 30th Annual IEEE Power Electronics Specialists Conference (PESC 99), Charleston, SC, USA, 1 July 1999; Volume 2, pp. 901–908. [Google Scholar] [CrossRef]

- Balogh, L. Paralleling Power-Choosing and Applying the Best Technique for Load Sharing. In Texas Instruments/UNITRODE Power Design Seminar SLUP207; Texas Instruments: Dallas, TX, USA, 2002; pp. 6-1–6-30. [Google Scholar]

- Vazquez, A.; Rodriguez, A.; Lamar, D.G.; Hernando, M.M. Advanced Control Techniques to Improve the Efficiency of IPOP Modular QSW-ZVS Converters. IEEE Trans. Power Electron. 2018, 33, 73–86. [Google Scholar] [CrossRef] [Green Version]

- Anand, S.; Fernandes, B. Modified droop controller for paralleling of DC-DC converters in standalone dc system. IET Power Electron. 2012, 5, 782–789. [Google Scholar] [CrossRef]

- Ahmad, U.; Cha, H.; Naseem, N. Integrated Current Balancing Transformer Based Input-Parallel Output-Parallel LLC Resonant Converter Modules. IEEE Trans. Power Electron. 2021, 36, 5278–5289. [Google Scholar] [CrossRef]

- Alemdar, O.S.; Keysan, O. Design and implementation of an unregulated DC-DC transformer (DCX) module using LLC resonant converter. In Proceedings of the 8th IET International Conference on Power Electronics, Machines and Drives (PEMD 2016), Glasgow, UK, 19–21 April 2016; pp. 1–6. [Google Scholar] [CrossRef]

- de Jesus Kremes, W.; Ewerling, M.V.M.; Illa Font, C.H.; Lazzarin, T.B. Analysis of Self-sharing of Currents in Steady-state of IPOP Connected Modular SEPIC Converter in DCM. In Proceedings of the 2018 9th IEEE International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Charlotte, NC, USA, 25–28 June 2018; pp. 1–7. [Google Scholar] [CrossRef]

- Duarte, C.; Barbi, I. A family of ZVS-PWM active-clamping DC-to-DC converters: Synthesis, analysis, design, and experimentation. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 1997, 44, 698–704. [Google Scholar] [CrossRef]

- De Jodar, E.; Villarejo, J.; Suardiaz, J.; Soto, F. Effect of the Output Impedance of Active Clamp Topology in Multiphase Converters. In Proceedings of the 2007 IEEE International Symposium on Industrial Electronics, Vigo, Spain, 4–7 June 2007; pp. 566–571. [Google Scholar] [CrossRef] [Green Version]

- Villarejo, J.; de Jodar, E.; Soto, F.; Moreno, M. Multistage Active-Clamp High Power Factor Rectifier with passive lossless current sharing. In Proceedings of the Energy Conversion Congress and Exposition, ECCE 2009, San Jose, CA, USA, 20–24 September 2009; pp. 948–953. [Google Scholar] [CrossRef]

- Spiazzi, G.; Mattavelli, P.; Costabeber, A. Effect of parasitic components in the integrated boost-flyback high step-up converter. In Proceedings of the 35th Annual Conference of IEEE Industrial Electronics (IECON ’09), Porto, Portugal, 3–5 November 2009; pp. 420–425. [Google Scholar] [CrossRef]

- Hren, A.; Korelic, J.; Milanovic, M. RC-RCD clamp circuit for ringing losses reduction in a flyback converter. IEEE Trans. Circuits Syst. Express Briefs 2006, 53, 369–373. [Google Scholar] [CrossRef]

- Duarte, C.; Barbi, I. An improved family of ZVS-PWM active-clamping DC-to-DC converters. IEEE Trans. Power Electron. 2002, 17, 1–7. [Google Scholar] [CrossRef]

- Masihuzzaman, M.; Lakshminarasamma, N. An improved ZVS-PWM, active clamp/reset forward converter: Analysis, design and dynamic model. In Proceedings of the IEEE 12th Workshop on Control and Modeling for Power Electronics (COMPEL), Boulder, CO, USA, 28–30 June 2010; pp. 1–8. [Google Scholar] [CrossRef]

- Spiazzi, G.; Mattavelli, P.; Costabeber, A. High Step-Up Ratio Flyback ConverterWith Active Clamp and Voltage Multiplier. IEEE Trans. Power Electron. 2011, 26, 3205–3214. [Google Scholar] [CrossRef]

- Bhardwaj, M.; Choudury, S. Digitally Controlled Solar Micro Inverter Design using C2000 Piccolo Microcontroller. In Texas Instruments User Guide TIDU405B; Texas Instruments: Dallas, TX, USA, 2017; pp. 1–54. [Google Scholar]

- Jimenez, J.M.; de Jodar, E.; Mateo, A.; Villarejo, J. Improving passive current sharing in multiphase active-clamp flyback converter with high step-up ratio. In Proceedings of the 19th European Conference on Power Electronics and Applications (EPE’17 ECCE Europe), Warsaw, Poland, 11–14 September 2017; pp. 1–7. [Google Scholar] [CrossRef]

- Watson, R.; Lee, F.; Hua, G. Utilization of an active-clamp circuit to achieve soft switching in flyback converters. IEEE Trans. Power Electron. 1996, 11, 162–169. [Google Scholar] [CrossRef]

| Parameters for the Output Voltage to Output Current Curves | ||

|---|---|---|

| V | : = 1:12 | |

| V | ||

| kHz | ||

| ns | 60 pF, 63 pF and 70 pF | |

| Components | Value-Reference | Description |

|---|---|---|

| MOSFET | IRFS4321 | N-channel 150 V; mΩ @ = 10 V |

| MOSFET | IRF6218S | P-channel V; 150 mΩ @ = V |

| MOSFET Driver | MCP14E4 | 4.0 A Dual H-Speed MOSFET Driver |

| Diode | C4D05120E | SiC Schottky; 1200 V, 9A |

| Diode clamp | MUR420 | Ultrafast; 200 V , 4 A |

| Coupled Inductors | Coilcraft KA-4823CL | 1:12; 28 ; 8 mΩ DCR@ = |

| Resonant Inductor | Coilcraft SER2010-102L | 1; mΩ DCR |

| Coilcraft SER2010-202L | 2; mΩ DCR | |

| Clamp Capacitor | F | 250 V |

| Output Capacitor | F | 630 V |

| Input Capacitor | 10F + | 63 V |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jiménez-Martínez, J.M.; de Jódar, E.; Villarejo, J. Parasitic Capacitance Effects on Active Clamp Flyback Output Characteristics: Application to IPOP Connection. Energies 2022, 15, 3201. https://0-doi-org.brum.beds.ac.uk/10.3390/en15093201

Jiménez-Martínez JM, de Jódar E, Villarejo J. Parasitic Capacitance Effects on Active Clamp Flyback Output Characteristics: Application to IPOP Connection. Energies. 2022; 15(9):3201. https://0-doi-org.brum.beds.ac.uk/10.3390/en15093201

Chicago/Turabian StyleJiménez-Martínez, Jacinto M., Esther de Jódar, and José Villarejo. 2022. "Parasitic Capacitance Effects on Active Clamp Flyback Output Characteristics: Application to IPOP Connection" Energies 15, no. 9: 3201. https://0-doi-org.brum.beds.ac.uk/10.3390/en15093201